Vật liệu đơn tinh thể cacbua silic (SiC) có độ rộng vùng cấm lớn (~Si 3 lần), độ dẫn nhiệt cao (~Si 3,3 lần hoặc GaAs 10 lần), tốc độ di chuyển bão hòa điện tử cao (~Si 2,5 lần), độ phóng điện cao trường (~Si 10 lần hoặc GaAs 5 lần) và các đặc tính nổi bật khác.

Các vật liệu bán dẫn thế hệ thứ ba chủ yếu bao gồm SiC, GaN, kim cương, v.v., vì độ rộng khe cấm (Eg) của nó lớn hơn hoặc bằng 2,3 electron volt (eV), còn được gọi là vật liệu bán dẫn khe rộng. So với vật liệu bán dẫn thế hệ thứ nhất và thứ hai, vật liệu bán dẫn thế hệ thứ ba có ưu điểm là độ dẫn nhiệt cao, điện trường phân hủy cao, tốc độ di chuyển electron bão hòa cao và năng lượng liên kết cao, có thể đáp ứng các yêu cầu mới của công nghệ điện tử hiện đại về hiệu suất cao. nhiệt độ, công suất cao, áp suất cao, tần số cao và khả năng chống bức xạ và các điều kiện khắc nghiệt khác. Nó có triển vọng ứng dụng quan trọng trong các lĩnh vực quốc phòng, hàng không, hàng không vũ trụ, thăm dò dầu khí, lưu trữ quang học, v.v. và có thể giảm hơn 50% tổn thất năng lượng trong nhiều ngành công nghiệp chiến lược như truyền thông băng thông rộng, năng lượng mặt trời, sản xuất ô tô, chiếu sáng bán dẫn và lưới điện thông minh, đồng thời có thể giảm hơn 75% khối lượng thiết bị, điều này có ý nghĩa quan trọng đối với sự phát triển của khoa học và công nghệ nhân loại.

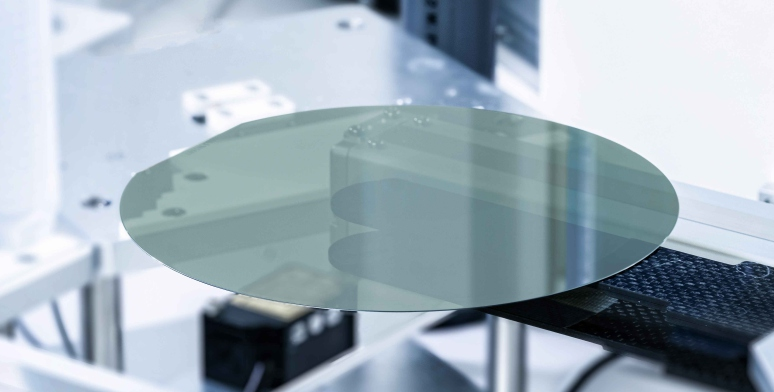

Năng lượng Semicera có thể cung cấp cho khách hàng chất nền cacbua silic dẫn điện (Dẫn điện), Bán cách điện (Bán cách điện), HPSI (Bán cách điện có độ tinh khiết cao); Ngoài ra, chúng tôi có thể cung cấp cho khách hàng các tấm epitaxy cacbua silic đồng nhất và không đồng nhất; Chúng tôi cũng có thể tùy chỉnh tấm epiticular theo nhu cầu cụ thể của khách hàng và không có số lượng đặt hàng tối thiểu.

THÔNG SỐ KỸ THUẬT

*n-Pm=n-loại Pm-Cấp,n-Ps=n-loại Ps-Cấp,Sl=bán cách điện

| Mục | 8 inch | 6 inch | 4 inch | ||

| nP | n-Pm | n-Ps | SI | SI | |

| TTV(GBIR) | 6um | 6um | |||

| Cung(GF3YFCD)-Giá trị tuyệt đối | 15μm | 15μm | 25μm | 15μm | |

| Cong vênh (GF3YFER) | 25μm | 25μm | 40μm | 25μm | |

| LTV(SBIR)-10mmx10mm | <2μm | ||||

| cạnh wafer | vát mép | ||||

HOÀN THIỆN BỀ MẶT

*n-Pm=n-loại Pm-Cấp,n-Ps=n-loại Ps-Cấp,Sl=Bán cách điện

| Mục | 8 inch | 6 inch | 4 inch | ||

| nP | n-Pm | n-Ps | SI | SI | |

| Hoàn thiện bề mặt | Đánh bóng quang học hai mặt,Si-Face CMP | ||||

| Độ nhám bề mặt | (10um x 10um) Si-FaceRa≤0,2nm Mặt C Ra< 0,5nm | (5umx5um) Si-Mặt Ra<0,2nm Mặt C Ra<0.5nm | |||

| Chip cạnh | Không được phép (chiều dài và chiều rộng ≥0,5mm) | ||||

| Thụt lề | Không được phép | ||||

| Vết xước (Si-Mặt) | Số lượng.<5, Tích lũy Chiều dài 0,5 × đường kính wafer | Số lượng.<5, Tích lũy Chiều dài 0,5 × đường kính wafer | Số lượng.<5, Tích lũy Chiều dài 0,5 × đường kính wafer | ||

| vết nứt | Không được phép | ||||

| Loại trừ cạnh | 3mm | ||||