Các thiết bị điện bán dẫn chiếm vị trí cốt lõi trong các hệ thống điện tử công suất, đặc biệt trong bối cảnh phát triển nhanh chóng của các công nghệ như trí tuệ nhân tạo, truyền thông 5G và phương tiện năng lượng mới, các yêu cầu về hiệu suất đối với chúng ngày càng được cải thiện.

cacbua silic(4H-SiC) đã trở thành vật liệu lý tưởng để chế tạo các thiết bị điện bán dẫn hiệu suất cao nhờ các ưu điểm như dải tần rộng, độ dẫn nhiệt cao, cường độ trường đánh thủng cao, tốc độ trôi bão hòa cao, tính ổn định hóa học và khả năng chống bức xạ. Tuy nhiên, 4H-SiC có độ cứng cao, độ giòn cao, độ trơ hóa học mạnh và độ khó xử lý cao. Chất lượng bề mặt của tấm nền wafer rất quan trọng đối với các ứng dụng thiết bị quy mô lớn.

Do đó, việc cải thiện chất lượng bề mặt của tấm nền 4H-SiC, đặc biệt là loại bỏ lớp bị hư hỏng trên bề mặt xử lý tấm bán dẫn, là chìa khóa để đạt được hiệu quả xử lý tấm nền 4H-SiC hiệu quả, ít tổn thất và chất lượng cao.

Cuộc thí nghiệm

Thí nghiệm sử dụng phôi 4H-SiC loại N 4 inch được trồng bằng phương pháp vận chuyển hơi vật lý, được xử lý thông qua cắt dây, mài, mài thô, mài mịn và đánh bóng, đồng thời ghi lại độ dày loại bỏ của bề mặt C và bề mặt Si và độ dày wafer cuối cùng trong mỗi quá trình.

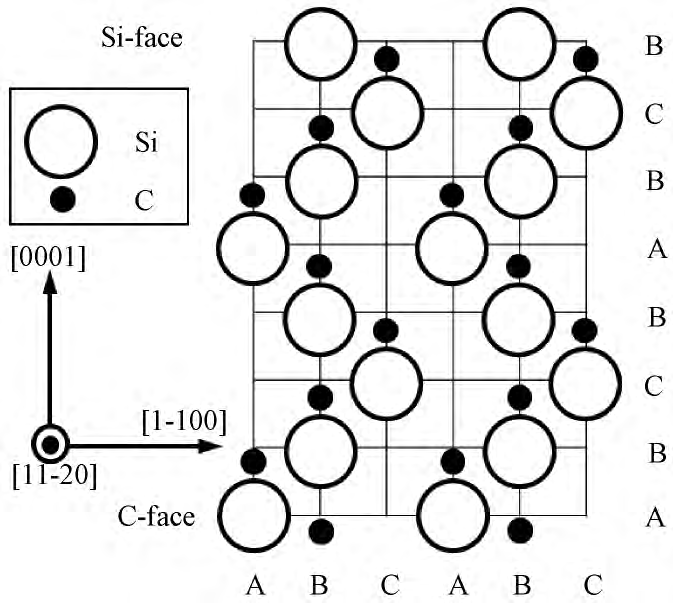

Hình 1 Sơ đồ cấu trúc tinh thể 4H-SiC

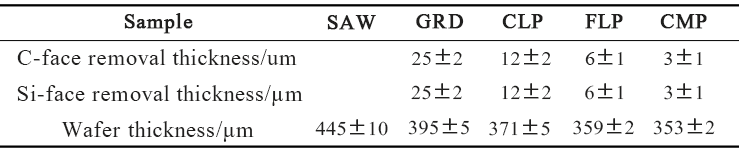

Hình 2 Độ dày được loại bỏ khỏi mặt C và mặt Si của 4H-tấm wafer SiCsau các bước xử lý khác nhau và độ dày của wafer sau khi xử lý

Độ dày, hình thái bề mặt, độ nhám và tính chất cơ học của tấm bán dẫn được đặc trưng đầy đủ bằng máy kiểm tra thông số hình học tấm bán dẫn, kính hiển vi giao thoa vi sai, kính hiển vi lực nguyên tử, dụng cụ đo độ nhám bề mặt và thiết bị đo nano. Ngoài ra, máy đo nhiễu xạ tia X có độ phân giải cao được sử dụng để đánh giá chất lượng tinh thể của tấm bán dẫn.

Các bước thử nghiệm và phương pháp thử nghiệm này cung cấp hỗ trợ kỹ thuật chi tiết để nghiên cứu tốc độ loại bỏ vật liệu và chất lượng bề mặt trong quá trình xử lý 4H-tấm wafer SiC.

Thông qua thí nghiệm, các nhà nghiên cứu đã phân tích sự thay đổi về tốc độ loại bỏ vật liệu (MRR), hình thái và độ nhám bề mặt cũng như tính chất cơ học và chất lượng tinh thể của 4H-tấm wafer SiCở các bước gia công khác nhau (cắt dây, mài, mài thô, mài mịn, đánh bóng).

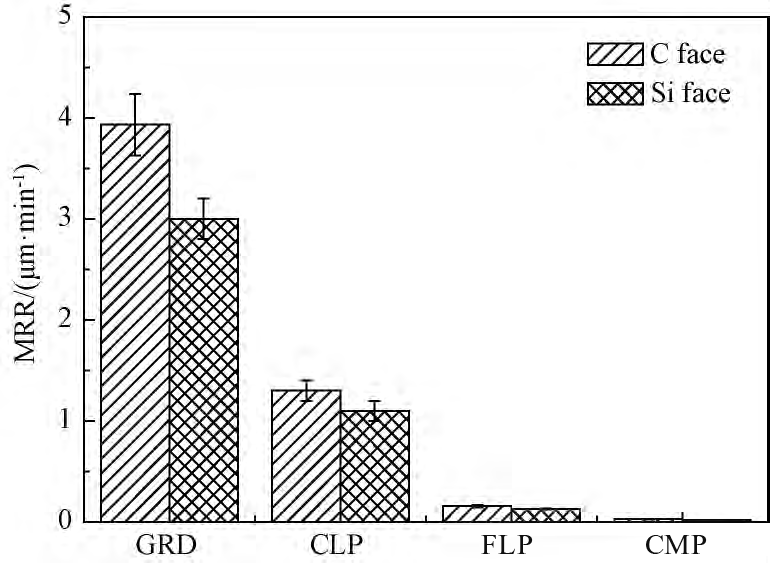

Hình 3 Tốc độ loại bỏ vật liệu của mặt C và mặt Si của 4H-tấm wafer SiCở các bước xử lý khác nhau

Nghiên cứu cho thấy do tính dị hướng về tính chất cơ học của các mặt tinh thể khác nhau của 4H-SiC, nên có sự khác biệt về MRR giữa mặt C và mặt Si trong cùng một quy trình và MRR của mặt C cao hơn đáng kể so với mặt tinh thể 4H-SiC. của Si-face. Với sự tiến bộ của các bước xử lý, hình thái bề mặt và độ nhám của tấm wafer 4H-SiC dần được tối ưu hóa. Sau khi đánh bóng, Ra của mặt C là 0,24nm và Ra của mặt Si đạt 0,14nm, có thể đáp ứng nhu cầu tăng trưởng epiticular.

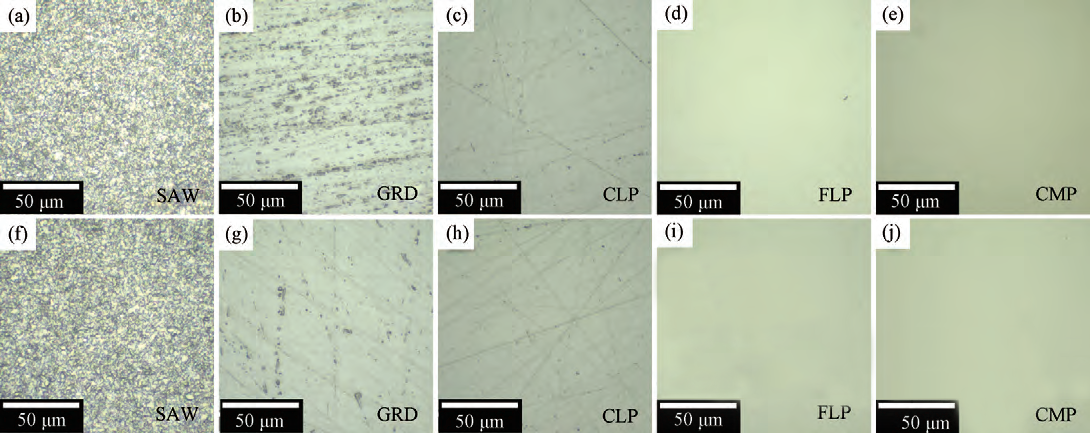

Hình 4 Hình ảnh kính hiển vi quang học của bề mặt C (a~e) và bề mặt Si (f~j) của tấm bán dẫn 4H-SiC sau các bước xử lý khác nhau

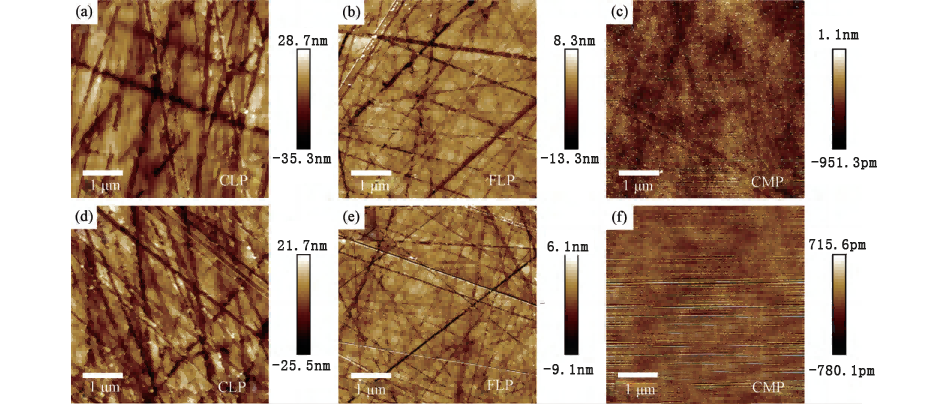

Hình 5 Hình ảnh kính hiển vi lực nguyên tử của bề mặt C (a~c) và bề mặt Si (d~f) của wafer 4H-SiC sau các bước xử lý CLP, FLP và CMP

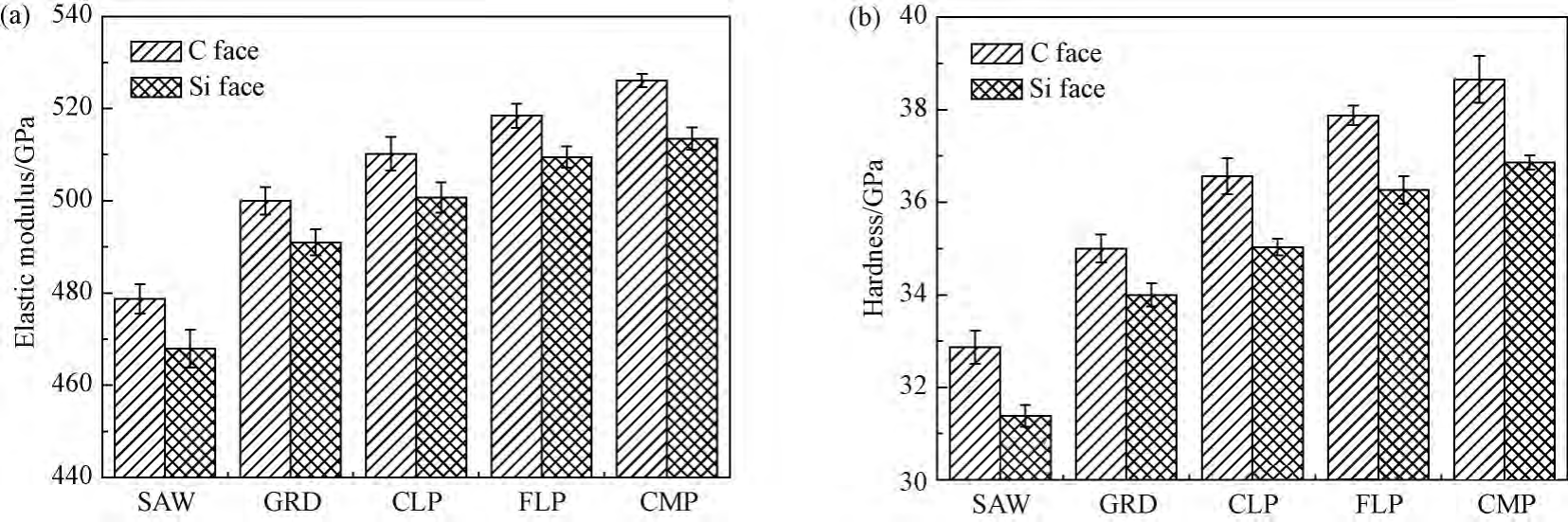

Hình 6 (a) mô đun đàn hồi và (b) độ cứng của bề mặt C và bề mặt Si của tấm wafer 4H-SiC sau các bước xử lý khác nhau

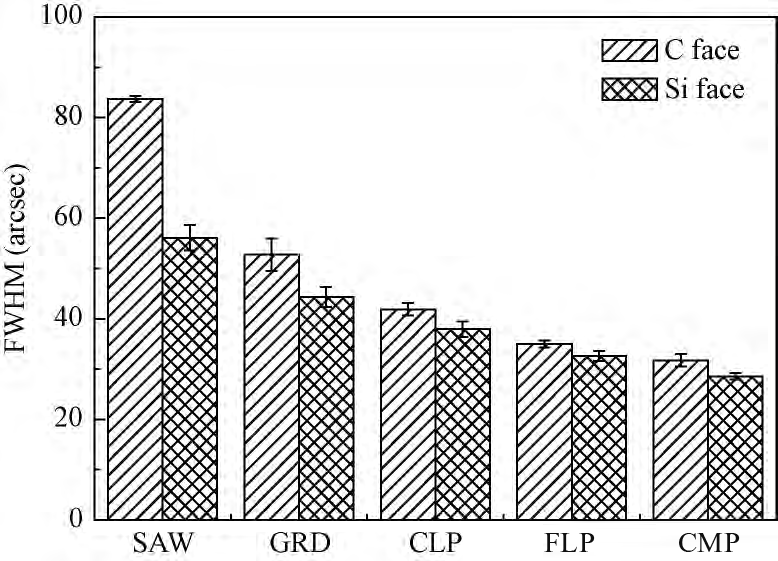

Thử nghiệm tính chất cơ học cho thấy bề mặt C của wafer có độ bền kém hơn vật liệu bề mặt Si, mức độ gãy giòn cao hơn trong quá trình xử lý, loại bỏ vật liệu nhanh hơn và hình thái và độ nhám bề mặt tương đối kém. Loại bỏ lớp hư hỏng trên bề mặt đã qua xử lý là chìa khóa để cải thiện chất lượng bề mặt của tấm bán dẫn. Chiều rộng nửa chiều cao của đường cong lắc lư 4H-SiC (0004) có thể được sử dụng để mô tả và phân tích một cách trực quan và chính xác lớp hư hỏng bề mặt của tấm bán dẫn.

Hình 7 (0004) nửa chiều rộng đường cong rung chuyển của mặt C và mặt Si của tấm wafer 4H-SiC sau các bước xử lý khác nhau

Kết quả nghiên cứu cho thấy lớp hư hỏng bề mặt của wafer có thể được loại bỏ dần dần sau khi xử lý wafer 4H-SiC, giúp cải thiện hiệu quả chất lượng bề mặt của wafer và cung cấp tài liệu tham khảo kỹ thuật để xử lý hiệu quả cao, tổn thất thấp và chất lượng cao của tấm nền 4H-SiC.

Các nhà nghiên cứu đã xử lý tấm wafer 4H-SiC thông qua các bước xử lý khác nhau như cắt dây, mài, mài thô, mài mịn và đánh bóng, đồng thời nghiên cứu ảnh hưởng của các quy trình này đến chất lượng bề mặt của tấm wafer.

Kết quả cho thấy với sự tiến bộ của các bước xử lý, hình thái bề mặt và độ nhám của tấm wafer dần được tối ưu hóa. Sau khi đánh bóng, độ nhám của mặt C và mặt Si lần lượt đạt 0,24nm và 0,14nm, đáp ứng yêu cầu tăng trưởng epiticular. Mặt C của wafer có độ dẻo dai kém hơn vật liệu mặt Si và dễ bị gãy giòn hơn trong quá trình xử lý, dẫn đến hình thái bề mặt tương đối kém và độ nhám. Loại bỏ lớp hư hỏng bề mặt của bề mặt đã được xử lý là chìa khóa để cải thiện chất lượng bề mặt của tấm bán dẫn. Nửa chiều rộng của đường cong lắc lư 4H-SiC (0004) có thể mô tả một cách trực quan và chính xác lớp hư hỏng bề mặt của tấm bán dẫn.

Nghiên cứu cho thấy rằng lớp hư hỏng trên bề mặt tấm wafer 4H-SiC có thể được loại bỏ dần dần thông qua quá trình xử lý tấm wafer 4H-SiC, cải thiện hiệu quả chất lượng bề mặt của tấm wafer, cung cấp tài liệu tham khảo kỹ thuật về hiệu suất cao, tổn thất thấp và hiệu suất cao. xử lý chất lượng của tấm nền 4H-SiC.

Thời gian đăng: Jul-08-2024