Tấm wafer là nguyên liệu chính để sản xuất mạch tích hợp, thiết bị bán dẫn rời rạc và thiết bị điện. Hơn 90% mạch tích hợp được chế tạo trên các tấm bán dẫn có độ tinh khiết cao, chất lượng cao.

Thiết bị chuẩn bị wafer đề cập đến quá trình chế tạo vật liệu silicon đa tinh thể nguyên chất thành vật liệu thanh đơn tinh thể silicon có đường kính và chiều dài nhất định, sau đó đưa vật liệu thanh đơn tinh thể silicon vào một loạt quá trình xử lý cơ học, xử lý hóa học và các quy trình khác.

Thiết bị sản xuất tấm silicon hoặc tấm silicon epiticular đáp ứng các yêu cầu về chất lượng bề mặt và độ chính xác hình học nhất định, đồng thời cung cấp chất nền silicon cần thiết cho sản xuất chip.

Quy trình điển hình để chuẩn bị các tấm silicon có đường kính nhỏ hơn 200 mm là:

Tăng trưởng đơn tinh thể → cắt ngắn → cán đường kính ngoài → cắt → vát → mài → khắc → mài mòn → đánh bóng → làm sạch → epit Wax → đóng gói, v.v.

Quy trình chính để chuẩn bị tấm silicon có đường kính 300 mm như sau:

Tăng trưởng đơn tinh thể → cắt ngắn → cán đường kính ngoài → cắt lát → vát cạnh → mài bề mặt → khắc → đánh bóng cạnh → đánh bóng hai mặt → đánh bóng một mặt → làm sạch lần cuối → epit Wax / ủ → đóng gói, v.v.

1. Chất liệu silicon

Silicon là vật liệu bán dẫn vì nó có 4 electron hóa trị và nằm trong nhóm IVA của bảng tuần hoàn cùng với các nguyên tố khác.

Số lượng electron hóa trị trong silicon đặt nó ở giữa chất dẫn điện tốt (1 electron hóa trị) và chất cách điện (8 electron hóa trị).

Silicon nguyên chất không có trong tự nhiên và phải được chiết xuất và tinh chế để đủ tinh khiết cho sản xuất. Nó thường được tìm thấy trong silica (silicon oxit hoặc SiO2) và các silicat khác.

Các dạng SiO2 khác bao gồm thủy tinh, tinh thể không màu, thạch anh, mã não và mắt mèo.

Vật liệu đầu tiên được sử dụng làm chất bán dẫn là germanium vào những năm 1940 và đầu những năm 1950, nhưng nó nhanh chóng được thay thế bằng silicon.

Silicon được chọn làm vật liệu bán dẫn chính vì bốn lý do chính:

Sự phong phú của vật liệu silicon: Silicon là nguyên tố phổ biến thứ hai trên Trái đất, chiếm 25% vỏ Trái đất.

Điểm nóng chảy cao hơn của vật liệu silicon cho phép dung sai quy trình rộng hơn: điểm nóng chảy của silicon ở 1412°C cao hơn nhiều so với điểm nóng chảy của germanium ở 937°C. Điểm nóng chảy cao hơn cho phép silicon chịu được các quá trình ở nhiệt độ cao.

Vật liệu silicon có phạm vi nhiệt độ hoạt động rộng hơn;

Sự phát triển tự nhiên của oxit silic (SiO2): SiO2 là vật liệu cách điện ổn định, chất lượng cao và đóng vai trò như một hàng rào hóa học tuyệt vời để bảo vệ silicon khỏi bị ô nhiễm từ bên ngoài. Độ ổn định về điện rất quan trọng để tránh rò rỉ giữa các dây dẫn liền kề trong mạch tích hợp. Khả năng tạo ra các lớp vật liệu SiO2 mỏng ổn định là nền tảng để sản xuất các thiết bị bán dẫn oxit kim loại (MOS-FET) hiệu suất cao. SiO2 có tính chất cơ học tương tự silicon, cho phép xử lý ở nhiệt độ cao mà không làm cong vênh tấm silicon quá mức.

2. Chuẩn bị wafer

Tấm bán dẫn được cắt từ vật liệu bán dẫn số lượng lớn. Vật liệu bán dẫn này được gọi là thanh tinh thể, được hình thành từ một khối lớn vật liệu nội tại đa tinh thể và không pha tạp.

Việc biến đổi một khối đa tinh thể thành một tinh thể đơn lớn và tạo cho nó sự định hướng tinh thể chính xác và lượng pha tạp loại N hoặc loại P thích hợp được gọi là sự tăng trưởng tinh thể.

Các công nghệ phổ biến nhất để sản xuất thỏi silicon đơn tinh thể để chuẩn bị tấm wafer silicon là phương pháp Czochralski và phương pháp nấu chảy vùng.

2.1 Phương pháp Czochralski và lò đơn tinh thể Czochralski

Phương pháp Czochralski (CZ), còn được gọi là phương pháp Czochralski (CZ), đề cập đến quá trình chuyển đổi chất lỏng silicon cấp bán dẫn nóng chảy thành các thỏi silicon đơn tinh thể rắn có định hướng tinh thể chính xác và pha tạp thành loại N hoặc P- kiểu.

Hiện tại, hơn 85% silicon đơn tinh thể được trồng bằng phương pháp Czochralski.

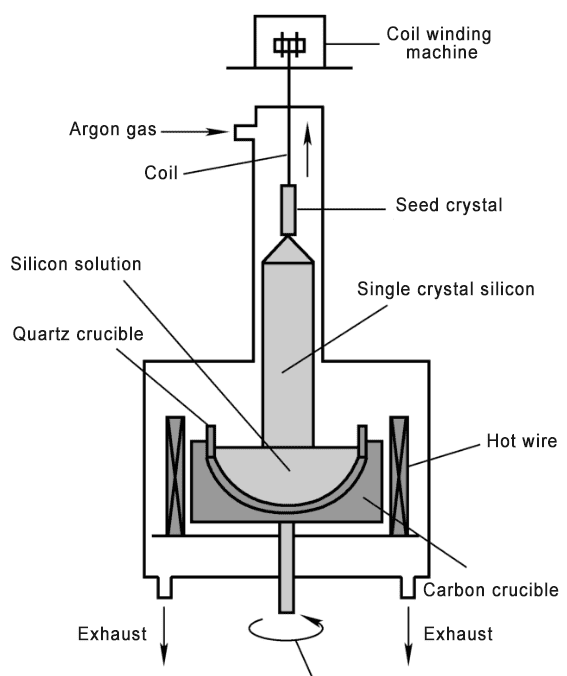

Lò nung đơn tinh thể Czochralski dùng để chỉ một thiết bị xử lý làm tan chảy vật liệu polysilicon có độ tinh khiết cao thành chất lỏng bằng cách nung nóng trong môi trường bảo vệ chân không cao hoặc khí hiếm (hoặc khí trơ), sau đó kết tinh lại chúng để tạo thành vật liệu silicon đơn tinh thể với một số chất bên ngoài nhất định. kích thước.

Nguyên lý làm việc của lò nung đơn tinh thể là quá trình vật lý của vật liệu silicon đa tinh thể kết tinh lại thành vật liệu silicon đơn tinh thể ở trạng thái lỏng.

Lò nung đơn tinh thể CZ có thể được chia thành bốn phần: thân lò, hệ thống truyền động cơ học, hệ thống kiểm soát nhiệt độ và sưởi ấm, và hệ thống truyền khí.

Thân lò bao gồm khoang lò, trục tinh thể hạt, nồi nấu kim loại thạch anh, thìa pha tạp, vỏ tinh thể hạt và cửa sổ quan sát.

Khoang lò đảm bảo nhiệt độ trong lò được phân bố đều và có thể tản nhiệt tốt; trục tinh thể hạt dùng để điều khiển tinh thể hạt di chuyển lên xuống và xoay; tạp chất cần pha tạp được cho vào thìa pha tạp;

Lớp vỏ tinh thể hạt có tác dụng bảo vệ tinh thể hạt khỏi bị nhiễm bẩn. Hệ thống truyền động cơ học chủ yếu được sử dụng để điều khiển chuyển động của tinh thể hạt và nồi nấu kim loại.

Để đảm bảo dung dịch silicon không bị oxy hóa, độ chân không trong lò phải rất cao, thường dưới 5 Torr và độ tinh khiết của khí trơ bổ sung phải trên 99,9999%.

Một mảnh silicon đơn tinh thể có hướng tinh thể mong muốn được sử dụng làm tinh thể hạt giống để phát triển phôi silicon và phôi silicon phát triển giống như một bản sao của tinh thể hạt giống.

Các điều kiện tại bề mặt tiếp xúc giữa silicon nóng chảy và tinh thể hạt silicon đơn tinh thể cần phải được kiểm soát chính xác. Những điều kiện này đảm bảo rằng lớp silicon mỏng có thể tái tạo chính xác cấu trúc của tinh thể mầm và cuối cùng phát triển thành một thỏi silicon đơn tinh thể lớn.

2.2 Phương pháp nấu chảy vùng và lò nung tinh thể đơn vùng

Phương pháp vùng nổi (FZ) tạo ra các thỏi silicon đơn tinh thể có hàm lượng oxy rất thấp. Phương pháp vùng nổi được phát triển vào những năm 1950 và có thể tạo ra silicon đơn tinh thể tinh khiết nhất cho đến nay.

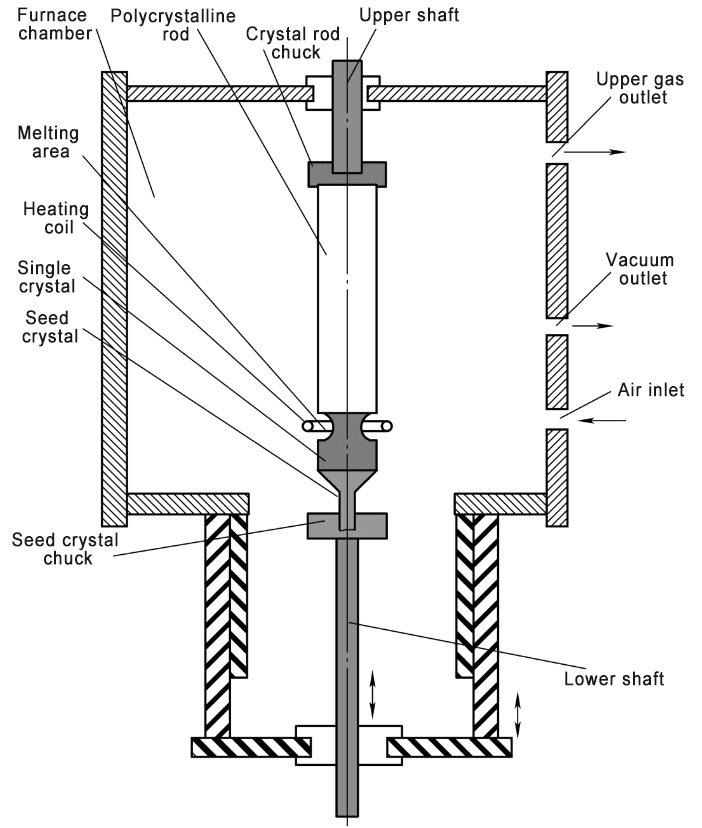

Lò nung đơn tinh thể vùng dùng để chỉ lò sử dụng nguyên lý nóng chảy vùng để tạo ra vùng nóng chảy hẹp trong thanh đa tinh thể thông qua khu vực kín hẹp nhiệt độ cao của thân lò thanh đa tinh thể trong chân không cao hoặc khí ống thạch anh hiếm môi trường bảo vệ.

Một thiết bị xử lý di chuyển một thanh đa tinh thể hoặc một thân lò nung để di chuyển vùng nóng chảy và dần dần kết tinh nó thành một thanh đơn tinh thể.

Đặc điểm của việc chuẩn bị các thanh đơn tinh thể bằng phương pháp nấu chảy vùng là độ tinh khiết của các thanh đa tinh thể có thể được cải thiện trong quá trình kết tinh thành các thanh đơn tinh thể và sự phát triển pha tạp của vật liệu thanh đồng đều hơn.

Các loại lò nung đơn tinh thể vùng có thể được chia thành hai loại: lò nung đơn tinh thể vùng nổi dựa vào sức căng bề mặt và lò nung đơn tinh thể vùng ngang. Trong các ứng dụng thực tế, lò nung đơn tinh thể vùng thường áp dụng phương pháp nấu chảy vùng nổi.

Lò nung đơn tinh thể vùng có thể chuẩn bị silicon đơn tinh thể có hàm lượng oxy thấp có độ tinh khiết cao mà không cần nồi nấu kim loại. Nó chủ yếu được sử dụng để điều chế silicon đơn tinh thể có điện trở suất cao (> 20kΩ·cm) và làm sạch silicon nóng chảy vùng. Những sản phẩm này chủ yếu được sử dụng trong sản xuất các thiết bị điện rời rạc.

Lò nung đơn tinh thể vùng bao gồm buồng lò, trục trên và trục dưới (bộ phận truyền động cơ học), mâm cặp thanh pha lê, mâm cặp tinh thể hạt, cuộn dây gia nhiệt (máy phát tần số cao), cổng khí (cổng chân không, đầu vào khí, đầu ra khí phía trên), v.v.

Trong kết cấu buồng lò có bố trí tuần hoàn nước làm mát. Đầu dưới của trục trên của lò đơn tinh thể là mâm cặp thanh pha lê, dùng để kẹp một thanh đa tinh thể; đầu trên của trục dưới là mâm cặp tinh thể hạt, dùng để kẹp tinh thể hạt.

Một nguồn điện tần số cao được cung cấp cho cuộn dây đốt nóng và một vùng nóng chảy hẹp được hình thành trong thanh đa tinh thể bắt đầu từ đầu dưới. Đồng thời, trục trên và trục dưới quay và hạ xuống, do đó vùng nóng chảy được kết tinh thành một tinh thể duy nhất.

Ưu điểm của lò nung đơn tinh thể vùng là nó không chỉ có thể cải thiện độ tinh khiết của đơn tinh thể đã chuẩn bị mà còn làm cho sự phát triển pha tạp của thanh đồng đều hơn và thanh đơn tinh thể có thể được tinh chế qua nhiều quy trình.

Nhược điểm của lò nung đơn tinh thể vùng là chi phí xử lý cao và đường kính nhỏ của tinh thể đơn đã chuẩn bị. Hiện nay, đường kính tối đa của tinh thể đơn có thể được chuẩn bị là 200mm.

Chiều cao tổng thể của thiết bị lò nung đơn tinh thể vùng tương đối cao và hành trình của trục trên và dưới tương đối dài, do đó có thể phát triển các thanh đơn tinh thể dài hơn.

3. Thiết bị và xử lý wafer

Thanh tinh thể cần trải qua một loạt quy trình để tạo thành chất nền silicon đáp ứng yêu cầu của sản xuất chất bán dẫn, cụ thể là tấm wafer. Quá trình xử lý cơ bản là:

Nhào lộn, cắt, cắt lát, ủ wafer, vát cạnh, mài, đánh bóng, làm sạch và đóng gói, v.v.

3.1 Ủ wafer

Trong quá trình sản xuất silicon đa tinh thể và silicon Czochralski, silicon đơn tinh thể có chứa oxy. Ở một nhiệt độ nhất định, oxy trong silicon đơn tinh thể sẽ tặng electron và oxy sẽ được chuyển thành chất cho oxy. Những electron này sẽ kết hợp với các tạp chất trong wafer silicon và ảnh hưởng đến điện trở suất của wafer silicon.

Lò ủ: dùng để chỉ lò làm tăng nhiệt độ trong lò lên 1000-1200°C trong môi trường hydro hoặc argon. Bằng cách giữ ấm và làm mát, oxy gần bề mặt của tấm wafer silicon được đánh bóng sẽ bay hơi và bị loại khỏi bề mặt của nó, khiến oxy kết tủa và tạo thành lớp.

Thiết bị xử lý hòa tan các khuyết tật vi mô trên bề mặt tấm silicon, giảm lượng tạp chất gần bề mặt tấm silicon, giảm khuyết tật và tạo thành một khu vực tương đối sạch trên bề mặt tấm silicon.

Lò ủ còn được gọi là lò nhiệt độ cao vì nhiệt độ cao. Ngành công nghiệp này còn gọi quá trình ủ wafer silicon là gettering.

Lò ủ wafer silicon được chia thành:

-Lò ủ nằm ngang;

-Lò ủ đứng;

-Lò ủ nhanh.

Sự khác biệt chính giữa lò ủ ngang và lò ủ dọc là hướng bố trí của buồng phản ứng.

Buồng phản ứng của lò ủ ngang có cấu trúc nằm ngang, và một loạt tấm silicon có thể được nạp vào buồng phản ứng của lò ủ để ủ cùng một lúc. Thời gian ủ thường là 20 đến 30 phút, nhưng buồng phản ứng cần thời gian gia nhiệt lâu hơn để đạt được nhiệt độ theo yêu cầu của quá trình ủ.

Quá trình của lò ủ dọc cũng áp dụng phương pháp nạp đồng thời một mẻ tấm silicon vào buồng phản ứng của lò ủ để xử lý ủ. Buồng phản ứng có bố cục cấu trúc thẳng đứng, cho phép đặt các tấm silicon trong thuyền thạch anh ở trạng thái nằm ngang.

Đồng thời, do thuyền thạch anh có thể quay toàn bộ trong buồng phản ứng nên nhiệt độ ủ của buồng phản ứng là đồng đều, sự phân bố nhiệt độ trên tấm wafer silicon là đồng đều và có đặc tính đồng nhất ủ tuyệt vời. Tuy nhiên, chi phí xử lý của lò ủ đứng cao hơn so với lò ủ ngang.

Lò ủ nhanh sử dụng đèn vonfram halogen để làm nóng trực tiếp tấm bán dẫn silicon, có thể làm nóng hoặc làm mát nhanh chóng trong phạm vi rộng từ 1 đến 250°C/s. Tốc độ gia nhiệt hoặc làm mát nhanh hơn so với lò ủ truyền thống. Chỉ mất vài giây để làm nóng nhiệt độ buồng phản ứng lên trên 1100°C.

————————————————————————————————————————————————————— ——

Semicera có thể cung cấpbộ phận than chì,nỉ mềm/cứng,bộ phận cacbua silic, Các bộ phận cacbua silic CVD, VàCác bộ phận được phủ SiC/TaCvới toàn bộ quá trình bán dẫn trong 30 ngày.

Nếu bạn quan tâm đến các sản phẩm bán dẫn trên, xin vui lòng liên hệ với chúng tôi ở lần đầu tiên.

ĐT: +86-13373889683

WhatsAPP: +86-15957878134

Email: sales01@semi-cera.com

Thời gian đăng: 26-08-2024