Trường ứng dụng

1. Mạch tích hợp tốc độ cao

2. Thiết bị vi sóng

3. Mạch tích hợp nhiệt độ cao

4. Thiết bị điện

5. Mạch tích hợp công suất thấp

6. MEMS

7. Mạch tích hợp điện áp thấp

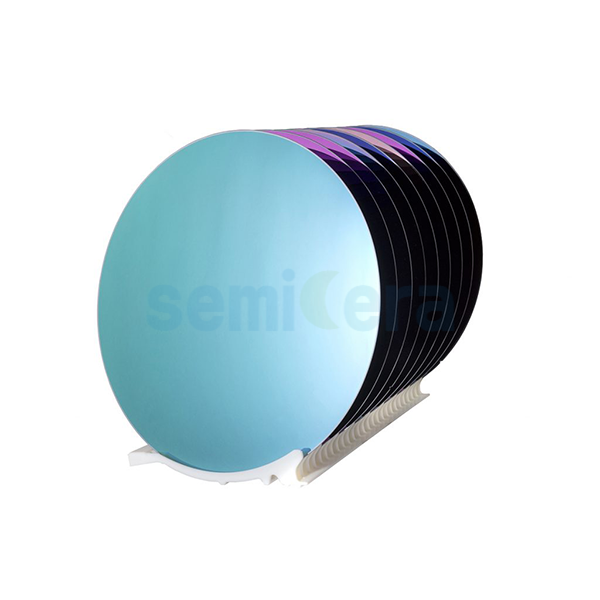

| Mục | Lý lẽ | |

| Tổng thể | Đường kính bánh xốp | 50/75/100/125/150/200mm±25um |

| Cung/Warp | <10um | |

| hạt | 0,3um <30ea | |

| Căn hộ / Notch | Bằng phẳng hoặc Notch | |

| Loại trừ cạnh | / | |

| Lớp thiết bị | Loại lớp thiết bị/Dopant | Loại N/Loại P |

| Định hướng lớp thiết bị | <1-0-0> / <1-1-1> / <1-1-0> | |

| Độ dày lớp thiết bị | 0,1 ~ 300um | |

| Điện trở lớp thiết bị | 0,001~100.000 ohm-cm | |

| Các hạt lớp thiết bị | <30ea@0.3 | |

| Lớp thiết bị TTV | <10um | |

| Kết thúc lớp thiết bị | đánh bóng | |

| HỘP | Độ dày oxit nhiệt chôn | 50nm(500Å)~15um |

| Lớp xử lý | Xử lý loại wafer/Dopant | Loại N/Loại P |

| Xử lý định hướng wafer | <1-0-0> / <1-1-1> / <1-1-0> | |

| Xử lý điện trở wafer | 0,001~100.000 ohm-cm | |

| Xử lý độ dày wafer | > 100um | |

| Xử lý kết thúc wafer | đánh bóng | |

| Tấm wafer SOI có thông số kỹ thuật mục tiêu có thể được tùy chỉnh theo yêu cầu của khách hàng. | ||